200G QSFP56 to 4×50G SFP56 Passive Direct Attach Copper Twinax Cable (DAC)

Compliant with SFF-8661、SFF-8432、IEEE 802.3bs-200GAUI-4、IEEE802.3cd-50GAUI-1、SFP-8636、SFF-8472 standard

Switch to Switch

Switch to GPU

- High Quality

- Factory Outlet

- Satisfaction Guarantee

- Global Shipping

| SPECIFICATIONS | |||

|---|---|---|---|

| Cable End Connector A | QSFP56 | Cable End Connector B | 4×SFP56 |

| Jumper Type | Active Optical Breakout Cable | Data Rate | 200G |

| Aggregate Bit Rate | 200Gbps | Lane Bit Rate | 50Gbps |

| Number of Channels | 4 | Single Channel Rate | 50G |

| Minimum Bend Radius | 5X Cable OD -Single, 10X Cable OD - Repeated | Factory Brand | PHILISUN |

| Attenuation | 26AWG:10dB/8.5m maximum 28AWG:10dB/7m maximum 30AWG:8.4dB/5.5m maximum | Bit Error Rate | ≤10-12 |

| Shield | Braid/Foil | Wire AWG | 26AWG/28AWG/30AWG |

| Cable Type | Passive Twinax | Cable OD | 30AWG: 7.8mm 28AWG: 7.0mm 26AWG: 7.0mm |

| Cable Colour/Material | Black PVC(OFNR) | Cable Length Selection | 0.5-3.5 meter |

| Protocols | SFF-8661/SFF-8432/IEEE 802.3bs-200GAUI-4/ IEEE802.3cd-50GAUI-1/SFP-8636/SFF-8472/SFF-8679 | Application Scenarios | 200Gigabit Ethernet (200GbE) |

| Supply Voltage | 3.3V | Power Dissipation | <0.1W |

| Operating Temperature | 0 to 70℃ (32 to 158℉) | Storage Temperature | -40 to 85℃ (-40 to 185℉) |

PRODUCT PRESENTATION

The PHILISUN 200G QSFP56 to 4x50G SFP56 Passive Direct Attach Copper Twinax Cable (DAC) is an essential Breakout Cable solution, converting a single 200G QSFP56 port into four independent 50G SFP56 channels. It is fully compliant with SFF-8661, SFF-8432, IEEE 802.3bs and IEEE 802.3cd standards, ensuring reliable performance in Data Center environments. This Passive Copper solution delivers Ultra-Low Latency and is highly Cost-Effective for maximizing port density, supporting scalable links from Switch to Switch and high-throughput connections from Switch to GPU servers.

DAC SERIES PRODUCTS

PRODUCTION & TESTING EQUIPMENT

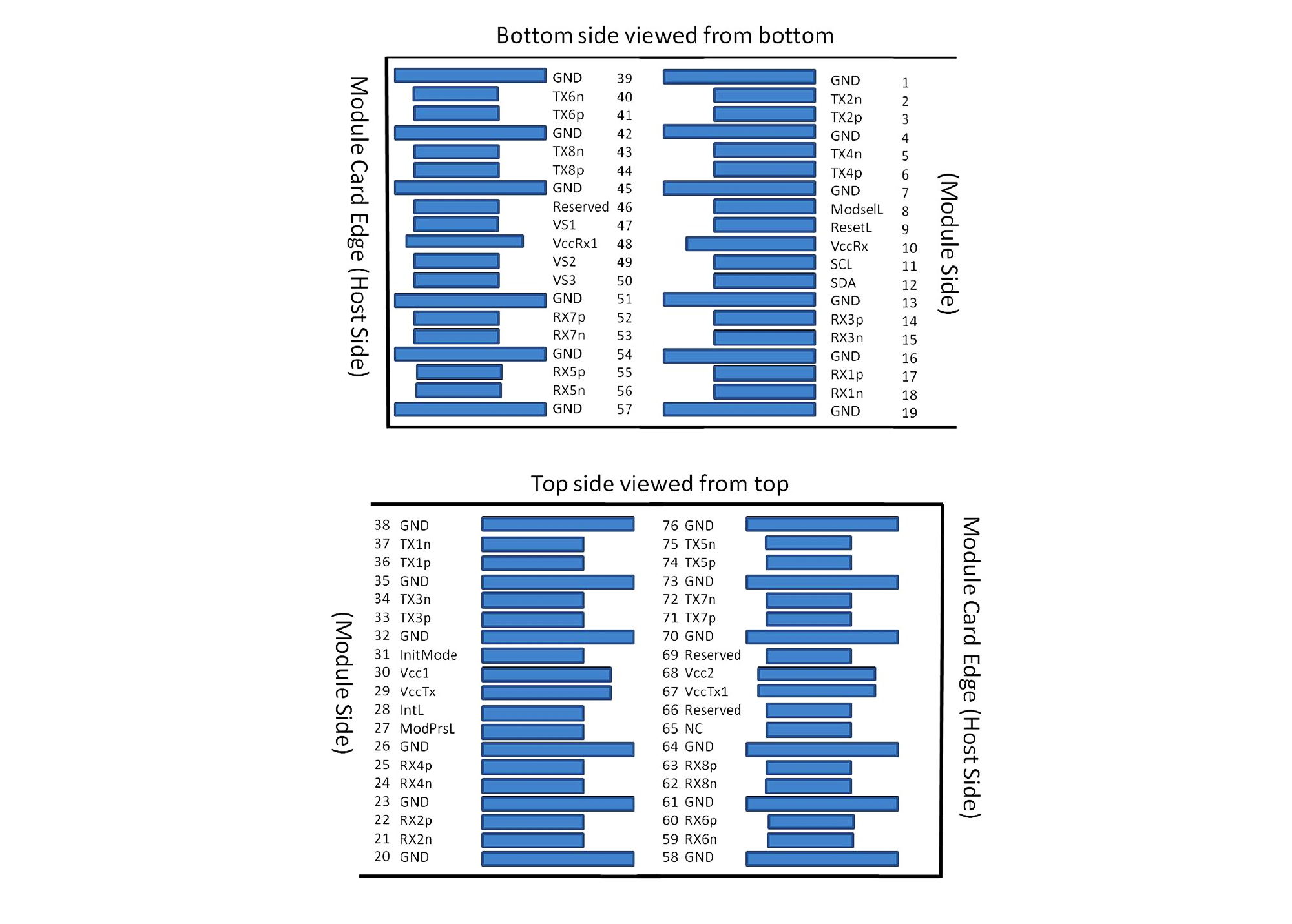

QSFP56 Pin Define

QSFP56 to 4×SFP56 Pin Function Definition

| PIN | Logic | Symbol | Description | Notes | |||||

| 1 | – | GND | Ground | 1 | |||||

| 2 | CML-I | Tx2n | Transmitter Inverted Data Input | – | |||||

| 3 | CML-I | Tx2p | Transmitter Non-Inverted Data Input | – | |||||

| 4 | – | GND | Ground | 1 | |||||

| 5 | CML-I | Tx4n | Transmitter Inverted Data Input | – | |||||

| 6 | CML-I | Tx4p | Transmitter Non-Inverted Data Input | – | |||||

| 7 | – | GND | Ground | 1 | |||||

| 8 | LVTTL-I | ModSelL | Module Select | – | |||||

| 9 | LVTTL-I | ResetL | Module Reset | – | |||||

| 10 | – | VccRx | +3.3 V Power Supply Receiver | 2 | |||||

| 11 | LVCMOS-I/O | SCL | 2-wire serial interface clock | – | |||||

| 12 | LVCMOS-I/O | SDA | 2-wire serial interface data | – | |||||

| 13 | – | GND | Ground | 1 | |||||

| 14 | CML-O | Rx3p | Receiver Non-Inverted Data Output | – | |||||

| 15 | CML-O | Rx3n | Receiver Inverted Data Output | – | |||||

| 16 | – | GND | Ground | 1 | |||||

| 17 | CML-O | Rx1p | Receiver Non-Inverted Data Output | – | |||||

| 18 | CML-O | Rx1n | Receiver Inverted Data Output | – | |||||

| 19 | – | GND | Ground | 1 | |||||

| 20 | – | GND | Ground | 1 | |||||

| 21 | CML-O | Rx2n | Receiver Inverted Data Output | – | |||||

| 22 | CML-O | Rx2p | Receiver Non-Inverted Data Output | – | |||||

| 23 | – | GND | Ground | 1 | |||||

| 24 | CML-O | Rx4n | Receiver Inverted Data Output | – | |||||

| 25 | CML-O | Rx4p | Receiver Non-Inverted Data Output | – | |||||

| 26 | – | GND | Ground | 1 | |||||

| 27 | LVTTL-O | ModPrsL | Module Present | – | |||||

| 28 | LVTTL-O | IntL | Interrupt | – | |||||

| 29 | – | VccTx | +3.3V Power supply transmitter | 2 | |||||

| 30 | – | Vcc1 | +3.3V Power supply | 2 | |||||

| 31 | LVTTL-I | InitMode | Initialization mode; In legacy QSFP applications, the InitMode pad is called LPMODE |

– | |||||

| 32 | – | GND | Ground | 1 | |||||

| 33 | CML-I | Tx3p | Transmitter Non-Inverted Data Input | – | |||||

| 34 | CML-I | Tx3n | Transmitter Inverted Data Input | – | |||||

| 35 | – | GND | Ground | 1 | |||||

| 36 | CML-I | Tx1p | Transmitter Non-Inverted Data Input | – | |||||

| 37 | CML-I | Tx1n | Transmitter Inverted Data Input | – | |||||

| 38 | – | GND | Ground | 1 | |||||

| 39 | – | GND | Ground | 1 | |||||

| 40 | CML-I | Tx6n | Transmitter Inverted Data Input | – | |||||

| 41 | CML-I | Tx6p | Transmitter Non-Inverted Data Input | – | |||||

| 42 | – | GND | Ground | 1 | |||||

| 43 | CML-I | Tx8n | Transmitter Inverted Data Input | – | |||||

| 44 | CML-I | Tx8p | Transmitter Non-Inverted Data Input | – | |||||

| 45 | – | GND | Ground | 1 | |||||

| 46 | – | Reserved | For future use | 3 | |||||

| 47 | – | VS1 | Module Vendor Specific 1 | 3 | |||||

| 48 | – | VccRx1 | 3.3V Power Supply | 2 | |||||

| 49 | – | VS2 | Module Vendor Specific 2 | 3 | |||||

| 50 | – | VS3 | Module Vendor Specific 3 | 3 | |||||

| 51 | – | GND | Ground | 1 | |||||

| 52 | CML-O | Rx7p | Receiver Non-Inverted Data Output | – | |||||

| 53 | CML-O | Rx7n | Receiver Inverted Data Output | – | |||||

| 54 | – | GND | Ground | 1 | |||||

| 55 | CML-O | Rx5p | Receiver Non-Inverted Data Output | – | |||||

| 56 | CML-O | Rx5n | Receiver Inverted Data Output | – | |||||

| 57 | – | GND | Ground | 1 | |||||

| 58 | – | GND | Ground | 1 | |||||

| 59 | CML-O | Rx6n | Receiver Inverted Data Output | – | |||||

| 60 | CML-O | Rx6p | Receiver Non-Inverted Data Output | – | |||||

| 61 | – | GND | Ground | 1 | |||||

| 62 | CML-O | Rx8n | Receiver Inverted Data Output | – | |||||

| 63 | CML-O | Rx8p | Receiver Non-Inverted Data Output | – | |||||

| 64 | – | GND | Ground | 1 | |||||

| 65 | – | NC | No Connect | 3 | |||||

| 66 | – | Reseved | For future use | 3 | |||||

| 67 | – | VccTx1 | 3.3V Power Supply | 2 | |||||

| 68 | – | Vcc2 | 3.3V Power Supply | 2 | |||||

| 69 | – | Reseved | For future use | 3 | |||||

| 70 | – | GND | Ground | 1 | |||||

| 71 | CML-I | Tx7p | Transmitter Non-Inverted Data Input | – | |||||

| 72 | CML-I | Tx7n | Transmitter Inverted Data Input | – | |||||

| 73 | – | GND | Ground | 1 | |||||

| 74 | CML-I | Tx5p | Transmitter Non-Inverted Data Input | – | |||||

| 75 | CML-I | Tx5n | Transmitter Inverted Data Input | – | |||||

| 76 | – | GND | Ground | 1 | |||||

| Notes: 1. QSFP56 TO 2 QSFP uses common ground (GND) for all signals and supply (power). All are common within the QSFP56 TO 2 QSFP module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signal-common ground plane. 2.VccRx, VccRx1, Vcc1, Vcc2, VccTx and VccTx1 shall be applied concurrently. Requirements defined for the host side of the Host Card Edge Connector are listed in Table 6. VccRx, VccRx1, Vcc1, Vcc2, VccTx and VccTx1 may be internally connected within the module in any combination. The connector Vcc pins are each rated for a maximum current of 1000 mA 3. All Vendor Specific, Reserved and No Connect pins may be terminated with 50 ohms to ground on the host. Pad 65 (No Connect) shall be left unconnected within the module. Vendor specific and Reserved pads shall have an impedance to GND that is greater than 10 kOhms and less than 100 pF. 4. Plug Sequence specifies the mating sequence of the host connector and module. The sequence is 1A, 2A, 3A, 1B, 2B, 3B. (see Figure 2 for pad locations) Contact sequence A will make, then break contact with additional QSFP56 TO 2 QSFP pads. Sequence 1A, 1B will then occur simultaneously, followed by 2A, 2B, followed by 3A,3B. |

|||||||||

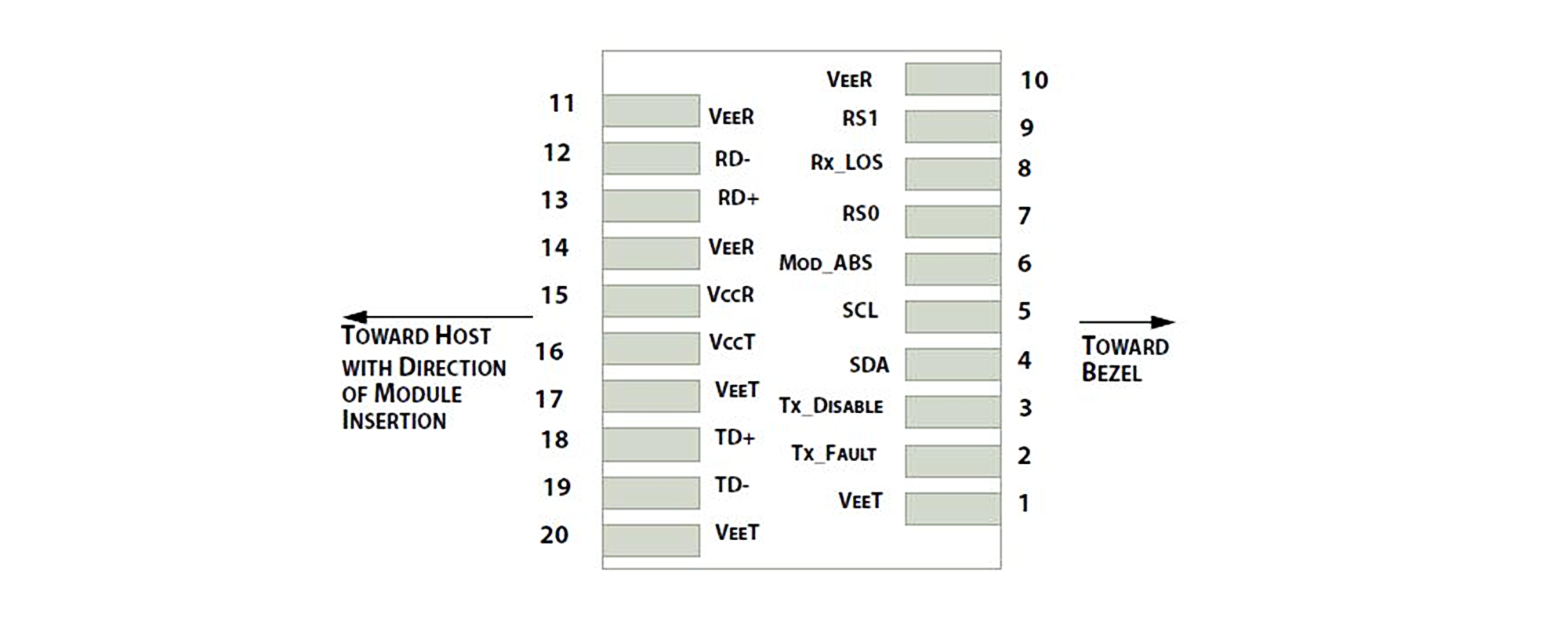

Host PCB SFP56 pad contact assignment

SFP56 Pin Descriptions

| Pin | Logic | Symbol | Description | Notes | |||||

| 1 | – | VeeT | Transmitter Ground | – | |||||

| 2 | – | TX_Fault | N/A | 1 | |||||

| 3 | LV-TTL-I | TX_DIS | Transmitter Disable | 2 | |||||

| 4 | LV-TTL-I/O | SDA | Tow Wire Serial Data | – | |||||

| 5 | LV-TTL-I | SCL | Tow Wire Serial | – | |||||

| 6 | MOD_DEF0 | Module present, | – | ||||||

| 7 | LV-TTL-I | RS0 | N/A | 1 | |||||

| 8 | LV-TTL-O | LOS | LOS of Signal | 2 | |||||

| 9 | LV-TTL-I | RS1 | N/A | 1 | |||||

| 10 | – | VeeR | Reciever Ground | – | |||||

| 11 | – | VeeR | Reciever Ground | – | |||||

| 12 | CML-O | RD- | Reciever Data Inverted | – | |||||

| 13 | CML-O | RD+ | Reciever Data | – | |||||

| 14 | – | VeeR | Reciever Ground | – | |||||

| 15 | – | VccR | Reciever Supply 3.3V | – | |||||

| 16 | – | VccT | Transmitter Supply | – | |||||

| 17 | – | VeeT | Transmitter Ground | – | |||||

| 18 | CML-I | TD+ | Transmitter Data | – | |||||

| 19 | CML_I | TD- | Transmitter Data | – | |||||

| 20 | – | VeeT | Transmitter Ground | – | |||||

| Notes: 1. Signals not supported in SFP56 Copper pulled-downto VeeT with 30K ohms resistor 2. Passive cable assemblies do not support LOS and TX_DIS |

|||||||||

PRODUCT CERTIFICATION

COMPATIBLE BRANDS

CONFIGURATION INFORMATION